# 16-channel High Voltage analog switch IC

ECN3298TF Product Specification

ECN3298 is 16-channel High Voltage analog switching IC with a bleed resistor on which latch-up free is realized by dielectric isolation technology.

Rev.1

High voltage and low ON-resistance MOS switches are used as output devices controlled by a 3.3V or 5V signal. The ECN3298 is most suited to Ultrasound Imaging applications.

### Functions

- \* High voltage and low on-resistance MOS switches integrated.

- \* 16bit shift resister integrated.

- \* Integrated bleed resistors on one side of the outputs.

\* Integrated clamping diodes for overvoltage protection positive overshoot. Features

- \* Switch on-resistance: 19  $\Omega$  typ. (VPP=100V,VNN=-100V,ISIG=5mA, 25°C)

- \* Switch breakdown voltage: 220V

- \* Latch-up free CMOS and High-Voltage drive circuit.

- \* Power up/down sequence of power supply is free.

- \* 48-pin TQFP Package (RoHS compliant)

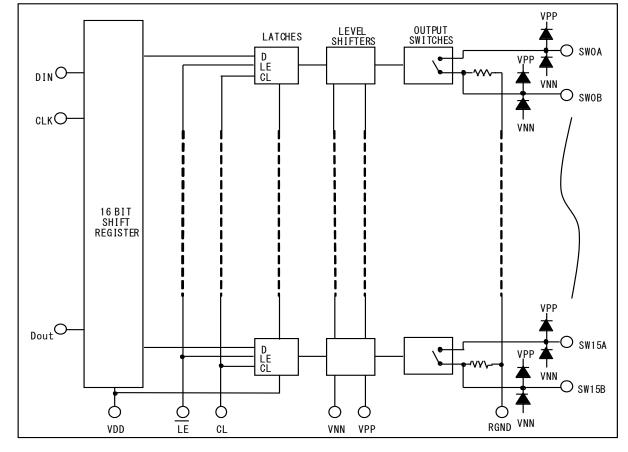

Fig.1 Block diagram

#### 1. General

This Specification shall be applied to the following semiconductor integrated circuit.

- 1) Parts name : ECN3298TF

- 2) Application : Ultrasound imaging scanner and others

- 3) Structure : Monolithic IC4) Package : TQFP48

### 2. Absolute Maximum Ratings

Table 1 Absolute Maximum Ratings

| No. | Items                            | Symbol Terminal |                    | Values          | Unit | Note              |

|-----|----------------------------------|-----------------|--------------------|-----------------|------|-------------------|

| 1   | Logic power supply voltage       | VDD             | VDD                | -0.5 to +7.0    | V    | Ta=25°C           |

| 2   | VPP-VNN supply voltage           | -               | VPP, VNN           | 220             | V    | Ta=25°C           |

| 3   | VPP Positive high voltage supply | VPP             | VPP                | -0.5 to 200     | V    | Ta=25°C           |

| 4   | VNN negative high voltage supply | VNN             | VNN                | -200 to +0.5    | V    | Ta=25°C           |

| 5   | Logic input voltages             | VDD             | DIN, CLK, CL<br>LE | -0.5 to VDD+0.3 | V    | Ta=25°C           |

| 6   | Analog signal range              | -               | SW0 to SW15        | VNN to VPP      | V    | Ta=25°C           |

| 7   | Operating junction temperature   | Тјор            | -                  | -20 to +125     | °C   |                   |

| 8   | Storage temperature              | Tstg            | -                  | -55 to +150     | °C   |                   |

| 9   | Power dissipation                | Pw              | -                  | 1.0             | W    | TQFP48<br>Ta=70°C |

### 3. Electrical Characteristics

3.1 DC Characteristics

|     | Та                                         | ble 2 D | C Chara | cteristics |     | -    | Ta=25°C                      | VDD=5V          |

|-----|--------------------------------------------|---------|---------|------------|-----|------|------------------------------|-----------------|

| No. | Items                                      | Symbol  |         | Spec       |     | Unit | Test o                       | onditions       |

| NO. | items                                      | Symbol  | Min     | Тур        | Max | Onic | 1631.0                       | onulions        |

|     |                                            |         | _       | 24         | 38  |      | ISIG=5mA                     | VPP=40V,        |

|     |                                            |         | _       | 17         | 27  |      | ISIG=200mA                   | VNN=-160V       |

| 1   | Small signal switch on                     | RONS    | _       | 19         | 27  | Ω    | ISIG=5mA                     | VPP=100V,       |

|     | resistance                                 | Rono    | —       | 15         | 24  | 22   | ISIG=200mA                   | VNN=-100V       |

|     |                                            |         | _       | 19         | 25  |      | ISIG=5mA                     | VPP=160V,       |

|     |                                            |         | -       | 15         | 25  |      | ISIG=200mA                   | VNN=-40V        |

| 2   | Small signal switch on resistance matching | ΔRONS   | _       | 5          | 20  | %    | VPP=100V, V<br>ISW=5mA       |                 |

| 3   | Large signal switch on resistance          | RONL    | _       | 16         | _   | Ω    | VPP=100V<br>VNN=-100V        | I SIG=1A        |

| 4   | Value of output bleed resistance           | RINT    | 20      | 35         | 50  | kΩ   | Output switch<br>IRINT=0.5mA | to RGND         |

| 5   | Switch off leakage per switch              | ISOL    | _       | 1.0        | 10  | μA   | VSIG=VPP-10<br>or VNN+10V    | )V,             |

| 6   | DC offset switch (off)                     | DCOFF   | _       | 10         | 100 | mV   | No load                      |                 |

| 7   | DC offset switch (on)                      | DCON    | -       | 10         | 100 | mV   | No load                      |                 |

| 8   | Positive HV supply current                 | IPPQ1   | -       | 10         | 50  | μA   | All SWs off                  |                 |

| 9   | Negative HV supply<br>current              | INNQ1   | _       | -10        | -50 | μA   | All SWs off                  |                 |

| 10  | Positive HV supply current                 | IPPQ2   | -       | 10         | 50  | μA   | All SWs on,                  | ISW=5mA         |

| 11  | Negative HV supply<br>current              | INNQ2   | _       | -10        | -50 | μA   | All SWs on,                  | ISW=5mA         |

|     |                                            |         | _       | _          | 7.0 |      | VPP=40V<br>VNN=-160V         | 50kHz<br>output |

| 12  | IPP Supply current                         | IPP     | _       | _          | 7.0 | mA   | VPP=100V<br>VNN=-100V        | switching       |

|     |                                            |         | _       | _          | 8.0 |      | VPP=160V<br>VNN=-40V         | without load    |

|     |                                            |         | _       | _          | 7.0 |      | VPP=40V<br>VNN=-160V         | 50kHz<br>output |

| 13  | INN Supply current                         | INN     | _       | _          | 7.0 | mA   | VPP=100V<br>VNN=-100V        | switching       |

|     |                                            |         | _       | _          | 8.0 |      | VPP=160V<br>VNN=-40V         | without load    |

| 14  | Logic supply average current               | IDD     | —       | -          | 4.0 | mA   | fCLK=5MHz,∖                  | 'DD=5.0V        |

| 15  | Logic supply quiescent<br>current          | IDDQ    | _       | _          | 10  | μA   |                              |                 |

| 16  | Data out source current                    | ISOR    | 0.45    | 0.70       | _   | mA   | VOUT=VDD-                    | 0.7V            |

| 17  | Data out sink current                      | ISINK   | 0.45    | 0.70       | _   | mA   | VOUT=0.7V                    |                 |

### 3.2 AC Characteristics

|     | Table 3 AC Characteristics   Ta=2 |        |                  |     |      |                 |                                           |  |  |

|-----|-----------------------------------|--------|------------------|-----|------|-----------------|-------------------------------------------|--|--|

| No. | Items                             | Symbol | Symbol Spec Unit |     |      | Test conditions |                                           |  |  |

| NO. | items                             | Symbol | Min              | Тур | Max  | Onit            |                                           |  |  |

| 1   | SW Turn on time                   | tON    | _                | _   | 5.0  | μS              | VSIG=VPP-10V, RL=10kΩ                     |  |  |

| 2   | SW Turn off time                  | tOFF   | -                | -   | 5.0  | μS              | VSIG=VPP-10V, RL=10kΩ                     |  |  |

| 3   | Clock frequency                   | fCLK   | _                | _   | 30   | MHz             | 50% duty cycle, fData=fCLK/2<br>VDD= 5.0V |  |  |

| 3   | Clock frequency                   | ICLK   | -                | _   | 20   | MHz             | 50% duty cycle, fData=fCLK/2<br>VDD=3.3V  |  |  |

| 4   | Clock delay time to<br>data out   | tDO    | 16               | -   | 55   | ns              | DOUT terminal,VDD=3.3V                    |  |  |

|     |                                   |        | 12               | -   | 42   | ns              | DOUT terminal, VDD=5.0V                   |  |  |

|     |                                   | +VSPK  | -                | -   | 150  |                 | VPP=40V, VNN=-160V,                       |  |  |

|     |                                   | -VSPK  | —                | -   | -150 |                 | RL=50Ω                                    |  |  |

| 5   | Output voltage spike              | +VSPK  | -                | -   | 150  | mV              | VPP=100V, VNN=-100V,                      |  |  |

| 5   | Output voltage spike              | -VSPK  | -                | -   | -150 | 111V            | RL=50Ω                                    |  |  |

|     |                                   | +VSPK  | -                | -   | 150  |                 | VPP=160V, VNN=-40V,                       |  |  |

|     |                                   | -VSPK  | _                | -   | -150 |                 | RL=50Ω                                    |  |  |

Table 4 AC Characteristics (for reference purpose only) Ta=

Ta=25°C VDD=5V

| No. | Items                       | Symbol    | Symbol |     |     |      | Condition                  |

|-----|-----------------------------|-----------|--------|-----|-----|------|----------------------------|

| NO. | items                       | Symbol    | Min    | Тур | Max | Unit | Condition                  |

| 1   | Off capacitance SW to GND   | CSG (off) | _      | 6   | -   | pF   | 0V, 1MHz                   |

| 2   | On Capacitance SW<br>to GND | CSG (on)  | -      | 15  | -   | pF   | 0V, 1MHz                   |

| 3   | SW off isolation            | КО        | -30    | -33 |     | dB   | fsw=5MHz, 1kΩ//15pF load   |

| 5   |                             | κυ        | -54    | -60 | -   | dB   | fsw=5MHz, 50 $\Omega$ load |

| 4   | SW Crosstalk                | KCR       | -54    | -60 | _   | dB   | fsw=5MHz, 50 $\Omega$ load |

Note: These items are not tested when shipped.

#### 4. Recommended Operating Conditions

Please operate in use within the limit of recommended operating conditions detailed in Table 5.

| No | Items                              | Symbol | Recommended Value         |

|----|------------------------------------|--------|---------------------------|

|    |                                    |        |                           |

| 1  | Logic power supply voltage         | VDD    | 3.0V to 5.5V              |

| 2  | Positive high voltage supply       | VPP    | 40V to 160V               |

| 3  | Negative high voltage supply       | VNN    | -160V to 0V               |

| 4  | VPP-VNN supply voltage             | -      | 40V to 200V               |

| 5  | High-level input voltage           | VIH    | 0.9VDD to VDD             |

| 6  | Low-level input voltage            | VIL    | 0V to 0.1VDD              |

| 7  | Analog signal voltage peak to peak | VSIG   | VNN to VPP                |

| 8  | Operating free air-temperature     | Та     | 0°C to 70°C               |

| 9  | Switching frequency                | Fsw    | 50kHz max, Duty Cycle=50% |

| 10 | Set up time for LE                 | TSD    | Min.60ns                  |

| 11 | Pulse width of LE                  | TWLE   | Min.40ns                  |

| 12 | Time width of CL                   | TWCL   | Min.40ns                  |

| 13 | Set up time DATA to Clock          | TSU    | Min.10ns                  |

| 14 | Hold time DATA from Clock          | Th     | Min.10ns                  |

| 15 | Maximum VSIG Slew Rate             | dV/dt  | Max.30V/ns                |

Table 5 Recommended Operating Conditions

Attention ;

1) Power up/down sequence of power supply is arbitrary except GND terminal of IC must be powered-up first and powered-down last.

2) It is indispensable to make there are not to exceed a maximum rated voltage by the occurrence of the excessive voltage in case of investing and cutting of the power supply.

### 5. Test Circuit

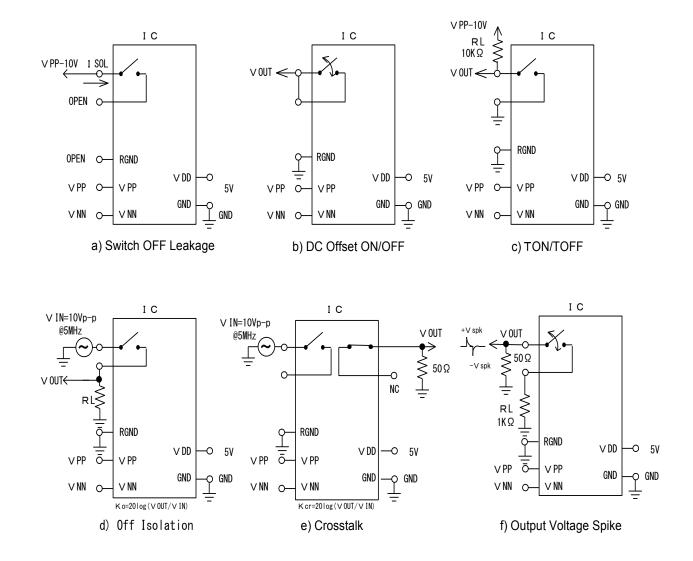

Fig. 2 Test Circuit

### 6. Timing Waveforms

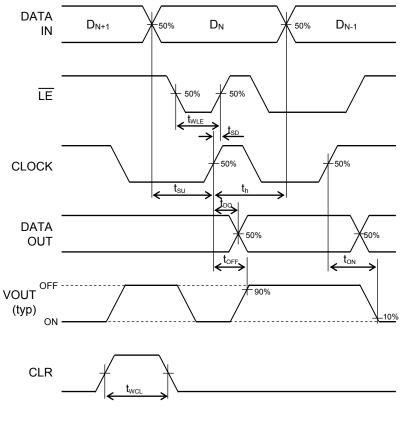

Fig. 3 Timing Waveforms

### <u>Note</u>

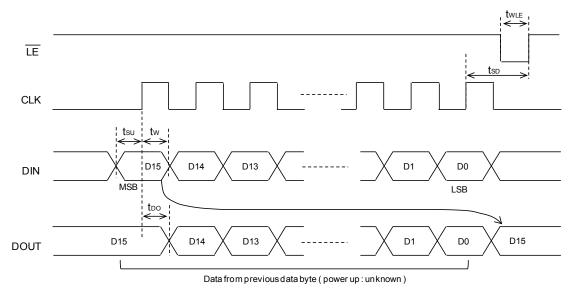

- 1. Serial data is clocked in on the rising edge of CLK.

- 2. The switches go to a state retaining their present condition on the rising edge of LE.

Fig. 4 LATCH ENABLE Timing waveform

### < ECN3298TF Product Specifications >

### 7. Truth Table

|              |    |     |          |     |     |     |     |             | able        | 6 Irl | ith tab | le   |            |           |           |      |      |

|--------------|----|-----|----------|-----|-----|-----|-----|-------------|-------------|-------|---------|------|------------|-----------|-----------|------|------|

| D0           | D1 | D2  | D3       | D4  | D5  | D6  | D7  | LE          | CL          | SW0   | SW1     | SW2  | SW3        | SW4       | SW5       | SW6  | SW7  |

| L            |    |     |          |     |     |     |     | L           | L           | OFF   |         |      |            |           |           |      |      |

| Н            |    |     |          |     |     |     |     | L           | L           | ON    |         |      |            |           |           |      |      |

|              | L  |     |          |     |     |     |     | L           | L           |       | OFF     |      |            |           |           |      |      |

|              | Н  |     |          |     |     |     |     | L           | L           |       | ON      |      |            |           |           |      |      |

|              |    | L   |          |     |     |     |     | L           | L           |       |         | OFF  |            |           |           |      |      |

|              |    | Н   |          |     |     |     |     | L           | L           |       |         | ON   |            |           |           |      |      |

|              |    |     | L        |     |     |     |     | L           | L           |       |         |      | OFF        |           |           |      |      |

|              |    |     | Н        |     |     |     |     | L           | L           |       |         |      | ON         |           |           |      |      |

|              |    |     |          | L   |     |     |     | L           | L           |       |         |      |            | OFF       |           |      |      |

|              |    |     |          | Н   |     |     |     | L           | L           |       |         |      |            | ON        |           |      |      |

|              |    |     |          |     | L   |     |     | L           | L           |       |         |      |            |           | OFF       |      |      |

|              |    |     |          |     | Н   |     |     | L           | L           |       |         |      |            |           | ON        |      |      |

|              |    |     |          |     |     | L   |     | L           | L           |       |         |      |            |           |           | OFF  |      |

|              |    |     |          |     |     | Н   |     | L           | L           |       |         |      |            |           |           | ON   |      |

|              |    |     |          |     |     |     | L   | L           | L           |       |         |      |            |           |           |      | OFF  |

|              |    |     |          |     |     |     | H   | L           | L           |       |         |      |            |           |           |      | ON   |

| X            | X  | X   | Х        | X   | X   | X   | X   | Н           | L           |       |         | r    | -          | IOUS S    | -         |      |      |

| Х            | Х  | Х   | Х        | Х   | Х   | Х   | Х   | Х           | Н           | OFF   | OFF     | OFF  | OFF        | OFF       | OFF       | OFF  | OFF  |

|              |    |     |          |     |     |     |     |             |             |       |         |      |            |           |           |      |      |

| D8           | D9 | D10 | D11      | D12 | D13 | D14 | D15 | LE          | CL          | SW8   | SW9     | SW10 | SW11       | SW12      | SW13      | SW14 | SW15 |

| L            |    |     |          |     |     |     |     | L           | L           | OFF   |         |      |            |           |           |      |      |

| Н            |    |     |          |     |     |     |     | L           | L           | ON    |         |      |            |           |           |      |      |

|              | L  |     |          |     |     |     |     | L           | L           |       | OFF     |      |            |           |           |      |      |

|              | Н  |     |          |     |     |     |     | L           | L           |       | ON      |      |            |           |           |      |      |

|              |    | L   |          |     |     |     |     | L           | L           |       |         | OFF  |            |           |           |      |      |

|              |    | Н   |          |     |     |     |     | L           | L           |       |         | ON   |            |           |           |      |      |

|              |    |     | L        |     | 1   |     |     | L           | L           |       |         |      | OFF        |           |           |      |      |

| 1            | 1  |     |          |     |     |     |     |             |             |       |         |      |            |           |           |      |      |

| <b>├</b> ─── |    |     | Н        |     |     |     |     | L           | L           |       |         |      | ON         |           |           |      |      |

|              |    |     | Н        | L   |     |     |     | L           | L           |       |         |      |            | OFF       |           |      |      |

|              |    |     | H        | L   |     |     |     | L<br>L      | L<br>L      |       |         |      |            | OFF<br>ON |           |      |      |

|              |    |     | <u>H</u> |     | L   |     |     | L<br>L<br>L | L<br>L<br>L |       |         |      |            |           | OFF       |      |      |

|              |    |     | H        |     | L   |     |     | L<br>L<br>L | L<br>L<br>L |       |         |      |            |           | OFF<br>ON |      |      |

|              |    |     | H        |     |     |     |     |             |             |       |         |      |            |           |           | OFF  |      |

|              |    |     | H        |     |     | L   |     |             |             |       |         |      |            |           |           | OFF  |      |

|              |    |     | H        |     |     |     |     |             |             |       |         |      |            |           |           |      | OFF  |

|              |    |     |          | H   | H   | H   | Н   |             |             |       |         |      | ON         | ON        | ON        |      | OFF  |

|              |    |     | H<br>    |     |     |     |     |             |             | OFF   | OFF     | HOLD | ON<br>PREV |           | ON        |      |      |

X = Don't care

<u>Note</u> 1. The 16 Switches operate independently.

2. When  $\overline{LE}$  is low, the shift register data flows through the latch.

3. Shift register clocking has no effect on the switch states if  $\overline{LE}$  is high. 4. When switch 15 is ON, DOUT is high. 5. The clear input overrides all other inputs.

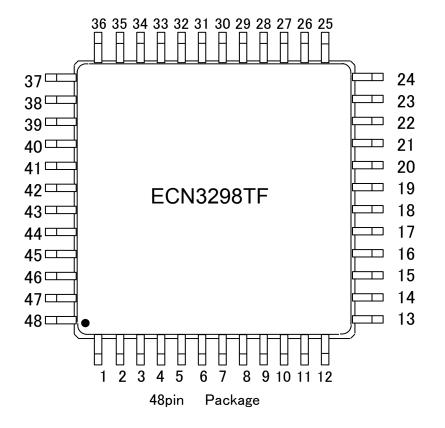

### 8. Pin Configuration

ECN3298TF TQFP48 (48Pin TQFP)

Table7. Pin Configuration

| Pin    | Name       | Functions                                           | Note |

|--------|------------|-----------------------------------------------------|------|

| 1      | N/C        | No connection.                                      | *1   |

| 2      | N/C        | No connection.                                      | *1   |

| 3      | SW4B       | Analog Switch 4 (Integrated output bleed resistor)  |      |

| 4      | SW4A       | Analog Switch 4                                     |      |

| 5      | SW3B       | Analog Switch 3 (Integrated output bleed resistor)  |      |

| 6      | SW3A       | Analog Switch 3                                     |      |

| 7      | SW2B       | Analog Switch 2 (Integrated output bleed resistor)  |      |

| 8      | SW2A       | Analog Switch 2                                     |      |

| 9      | SW1B       | Analog Switch 1 (Integrated output bleed resistor)  |      |

| 10     | SW1A       | Analog Switch 1                                     |      |

| 11     | SW0B       | Analog Switch 0 (Integrated output bleed resistor)  |      |

| 12     | SW0A       | Analog Switch 0                                     |      |

| 13     | VNN        | Negative High Voltage Supply.                       | *2   |

| 14     | N/C        | No connection.                                      | *1   |

| 15     | VPP        | Positive High Voltage Supply.                       | *2   |

| 16     | N/C        | No connection.                                      | *1   |

| 17     | GND        | Ground                                              |      |

| 18     | VDD        | Logic Supply Voltage                                |      |

| 19     | DIN        | Serial Data Input                                   |      |

| 20     | CLK        | Serial Clock Input                                  |      |

| 21     | LE         | Latch-Enable Input                                  |      |

| 22     | CLR        | Latch-Clear Input                                   |      |

| 23     | DOUT       | Serial Data Output                                  |      |

| 24     | RGND       | Ground. Connect to Bleed Resister.                  | *3   |

| 25     | SW15B      | Analog Switch 15 (Integrated output bleed resistor) |      |

| 26     | SW15A      | Analog Switch 15                                    |      |

| 27     | SW14B      | Analog Switch 14 (Integrated output bleed resistor) |      |

| 28     | SW14A      | Analog Switch 14                                    |      |

| 29     | SW13B      | Analog Switch 13 (Integrated output bleed resistor) |      |

| 30     | SW13A      | Analog Switch 13                                    |      |

| 31     | SW12B      | Analog Switch 12 (Integrated output bleed resistor) |      |

| 32     | SW12A      | Analog Switch 12                                    |      |

| 33     | SW11B      | Analog Switch 11 (Integrated output bleed resistor) |      |

| 34     | SW11A      | Analog Switch 11                                    |      |

| 35     | N/C        | No connection.                                      | *1   |

| 36     | N/C        | No connection.                                      | *1   |

| 37     | SW10B      | Analog Switch 10 (Integrated output bleed resistor) |      |

| 38     | SW10A      | Analog Switch 10                                    |      |

| 39     | SW9B       | Analog Switch 9 (Integrated output bleed resistor)  |      |

| 40     | SW9A       | Analog Switch 9                                     |      |

| 41     | SW8B       | Analog Switch 8 (Integrated output bleed resistor)  |      |

| 42     | SW8A       | Analog Switch 8                                     |      |

| 43     | SW7B       | Analog Switch 7 (Integrated output bleed resistor)  |      |

| 44     | SW7A       | Analog Switch 7                                     |      |

| 45     | SW6B       | Analog Switch 6 (Integrated output bleed resistor)  |      |

| 46     | SW6A       | Analog Switch 6                                     |      |

| 47     | SW5B       | Analog Switch 5 (Integrated output bleed resistor)  |      |

| 48     | SW5A       | Analog Switch 5                                     |      |

| Note 1 | I. NOT con | nected on chip internal.                            |      |

2. High voltage supply.

3. Connected all SW\_B terminals with a bleed resistor on chip internal.

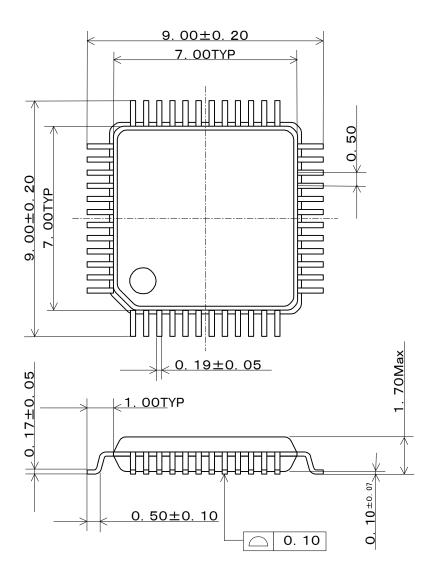

### 9. Package Outline

Units : mm

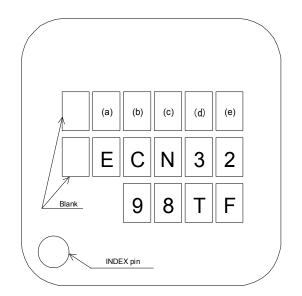

Lot numbering rule

(a) :Year code (Least significant digit of Assembled year (A.D.))

(b) :Month code (Refer to following table.)

| Month         | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

|---------------|---|---|---|---|---|---|---|---|---|----|----|----|

| Month<br>code | A | В | С | D | E | к | L | Μ | Ν | х  | Y  | Z  |

(c),(d),(e) :Serial number within year/month code

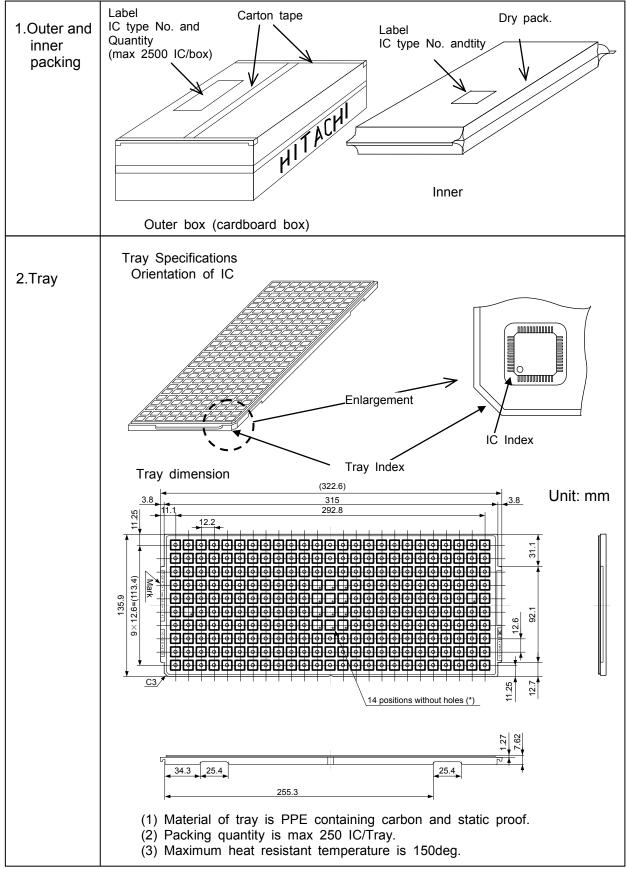

### 11 Packing Form

Packaging details are as shown below.

#### 12 Inspection

Hundred percent inspections shall be conducted on electric characteristics.

#### 13. Precautions for use

- 13.1 Countermeasures against Electrostatic Discharge (ESD)

- (a) Customers need to take precautions to protect ICs from electrostatic discharge (ESD). The material of the container or any other device used to carry ICs should be free from ESD, which can be caused by vibration during transportation. Use of electrically conductive containers is recommended as an effective countermeasure.

- (b) Everything that touches ICs, such as the work platform, machine, measuring equipment, and test equipment, should be grounded.

- (c) Workers should be high-impedance grounded ( $100k\Omega$  to  $1M\Omega$ ) while working with ICs, to avoid damaging the ICs by ESD.

- (d) Friction with other materials, such as high polymers, should be avoided.

- (e) When carrying a PCB with a mounted IC, ensure that the electric potential is maintained at a constant level using the short-circuit terminals and that there is no vibration or friction.

- (f) The humidity at an assembly line where ICs are mounted on circuit boards should be kept around 45 to 75 percent using humidifiers or such. If the humidity cannot be controlled effectively, using ionized air blowers (ionizers) is effective.

#### 13.2 Output Short-Circuit Protection

A short circuit (ex. load short) could damage this IC (the product of Hitachi Power Semiconductor Device, hereinafter called "HPSD's IC"). External protection is needed to prevent HPSD's IC breakdown.

#### 13.3 Maximum ratings

Regardless of changes in external conditions during use HPSD's IC, the "maximum ratings" described in this document should never be exceeded when designing electronic circuits that employ HPSD's IC. If maximum ratings are exceeded, HPSD's IC may be damaged or destroyed. In no event shall Hitachi Power Semiconductor Device (hereinafter called "HPSD") be liable for any failure in HPSD's IC or any secondary damage resulting from use at a value exceeding the maximum ratings.

#### 13.4 Derating Design

Continuous high-load operation (high temperatures, high voltages, large currents) should be avoided and derating design should be applied, even within the ranges of the maximum ratings, to ensure reliability.

#### 13.5 Safe Design

The HPSD's IC may fail due to accidents or unexpected surge voltages. Accordingly, adopt safe design features, such as redundancy and measures to prevent misuse, in order to avoid extensive damage in the event of a failure.

#### 13.6 Application

If HPSD's IC is applied to the following uses where high reliability is required, obtain the document of permission from HPSD in advance.

· Automobile, Train, Vessel, etc.

Do not apply HPSD's IC to the following uses where extremely high reliability is required.

Nuclear power control system, Aerospace instrument, Life-support-related medical equipment, etc.

#### 13.7 Soldering

Lead-free solder is used for coating pins and the tab of this IC. Refer to "Instructions for Use of Hitachi High-Voltage Monolithic ICs" for soldering conditions.

#### 13.8 Others

See "Instructions for Use of Hitachi High-Voltage Monolithic ICs" for other precautions and instructions on how to deal with these kinds of products.

#### 14. Usage

- (1) HPSD warrants that the HPSD products have the specified performance according to the respective specifications at the time of its sale. Testing and other quality control techniques of the HPSD products by HPSD are utilized to the extent HPSD needs to meet the specifications described in this document. Not every device of the HPSD products is specifically tested on all parameters, except those mandated by relevant laws and/or regulations.

- (2) Following any claim regarding the failure of a product to meet the performance described in this document made within one month of product delivery, all the products in relevant lot(s) shall be re-tested and re-delivered. The HPSD products delivered more than one month before such a claim shall not be counted for such response.

- (3) HPSD assumes no obligation nor makes any promise of compensation for any fault which should be found in a customer's goods incorporating the products in the market. If a product failure occurs for reasons obviously attributable to HPSD and a claim is made within six months of product delivery, HPSD shall offer free replacement or payment of compensation. The maximum compensation shall be the amount paid for the products, and HPSD shall not assume responsibility for any other compensation.

- (4) HPSD reserves the right to make changes in this document and to discontinue mass production of the relevant products without notice. Customers are advised to confirm specification of the product of inquiry before purchasing of the products that the customer desired. Customers are further advised to confirm before purchasing of such above products that the product of inquiry is the latest version and that the relevant product is in mass production status if the purchasing of the products by the customer is suspended for one year or more.

- (5) When you dispose of HPSD products and/or packing materials, comply with the laws and regulations of each country and/or local government. Conduct careful preliminary studies about environmental laws applying to your products such as RoHS, REACH. HPSD shall not assume responsibility for compensation due to contravention of laws and/or regulations.

- (6) HPSD shall not be held liable in any way for damages and infringement of patent rights, copyright or other intellectual property rights arising from or related to the use of the information, products, and circuits in this document.

- (7) No license is granted by this document of any patents, copyright or other intellectual property rights of any third party or of HPSD.

- (8) This document may not be reprinted, reproduced or duplicated, in any form, in whole or in part without the express written permission of HPSD.

- (9) You shall not use the HPSD products (technologies) described in this document and any other products (technologies) manufactured or developed by using them (hereinafter called "END Products") or supply the HPSD products (technologies) and END Products for the purpose of disturbing international peace and safety, including (i) the design, development, production, stockpiling or any use of weapons of mass destruction such as nuclear, chemical or biological weapons or missiles, (ii) the other military activities, or (iii) any use supporting these activities. You shall not sell, export, dispose of, license, rent, transfer, disclose or otherwise provide the HPSD products (technologies) and END Products to any third party whether directly or indirectly with knowledge or reason to know that the third party or any other party will engage in the activities described above. When exporting, re-export transshipping or otherwise transferring the HPSD products (technologies) and END

When exporting, re-export transchipping or otherwise transferring the HPSD products (technologies) and END Products, all necessary procedures are to be taken in accordance with Foreign Exchange and Foreign Trade Act (Foreign Exchange Act) of Japan, Export Administration Regulations (EAR) of US, and any other applicable export control laws and regulations promulgated and administered by the governments of the countries asserting jurisdictions over the parties or transaction.

### Appendix-Supplementary Data

Please read below contents before using this product.

Function Discription

1. Bleed resistor

ECN3298TF feature integrated  $35k\Omega$  bleed resistor to discharge capacitive Loads such as piezoelectric transducers. One side of analog switch terminal(SW\_B) is coneccted RGND with ableed resistor.

2. Overvoltage Protection

ECN3298<sup>T</sup>F feature clamping diodes to protect circuit against the overvoltage exceed VPP or VNN. ALL analog switches connect VPP and VNN terminals with clamping diode. Normaly, switch input voltage must not exceed VNN and VPP, and maximum current flows through the clamping diode should be less than 1A.

#### 3. Power supply seaquence

ECN3298TF doesn't require special sequencing of the VPP, VNN, and VDD supply voltages. However, logic state is unsettled when power-up. After power-up, please refer to the truth tabl e(Page.7 Table.7) and set the data of shift register.

### Precautions for Safe Use and Notices

If semiconductor devices are handled inappropriate manner, failures may result. For this reason, be sure to read "Precaution for Use" before use.

Image: This mark indicates an item about which caution is required.

Image: CAUTION

This mark indicates a potentially hazardous situation which, if not avoided, may result in minor or moderate injury and damage to property.

**CAUTION** (1) Regardless of changes in external conditions during use "absolute maximum ratings" should never be exceed in designing electronic circuits that employ semiconductors. In the case of pulse use, furthermore,"safe operating area (SOA)"precautions should be observed. (2) Semiconductor devices may experience failures due to accident or unexpected surge voltages. Accordingly, adopt safe design features, such as redundancy or prevention of erroneous action, to avoid extensive damage in the event of a failure. (3) In cases where extremely high reliability is required (such as use in nuclear power control, aerospace and aviation, traffic equipment, life-support-related medical equipment, fuel control equipment and various kinds of safety equipment), safety should be ensured by using semiconductor devices that feature assured safety or by means of user's fail-safe precautions or other arrangement. Or consult Hitachi's sales department staff. (If a semiconductor devices fails, there may be cases in which the semiconductor device, wiring or wiring pattern will emit smoke or cause a fire or in which the semiconductor device will burst)

## NOTICES

- 1. This Data sheet contains the specifications, characteristics (in figures and tables), dimensions and handling notes concerning power semiconductor products (hereinafter called "products") to aid in the selection of suitable products.

- 2. The specifications and dimensions, etc. stated in this Data sheet are subject to change without prior notice to improve products characteristics. Before ordering, purchasers are advised to contact Hitachi's sales department for the latest version of this Data sheet and specifications.

- 3. In no event shall Hitachi be liable for any damage that may result from an accident or any other cause during operation of the user's units according to this Data sheet. Hitachi assumes to responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in this Data sheet.

- 4. In no event shall Hitachi be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.

- 5. No license is granted by this Data sheet under any patents or other rights of any third party or Hitachi, Ltd.

- 6. This Data sheet may not be reproduced or duplicated, in any form, in whole or in part, without the expressed written permission of Hitachi, Ltd.

- 7. The products (technologies) described in this Data sheet are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.