8-ch High Voltage Analog Switching IC

# ECN3290TF/PL/FN

ECN3290 is an eight-channel High Voltage analog switching IC on which latch-up free is realized by dielectric isolation technology.

High voltage and low ON-resistance MOS switches are used as output devices controlled by a 5V signal. The ECN3290 is most suited to Ultrasound Imaging applications.

### Functions

- · High voltage and low on-resistance MOS switches integrated.

- 8bit shift resister integrated.

### Features

- Switch on-resistance: 22 Ω typ. (VPP=100V,VNN=-100V, ISIG=5mA, 25°C)

- · Switch breakdown voltage: 220V

- · Latch-up free CMOS and High-Voltage drive circuit.

- · Power up/down sequence of power supply is free.

- RoHS Compliant

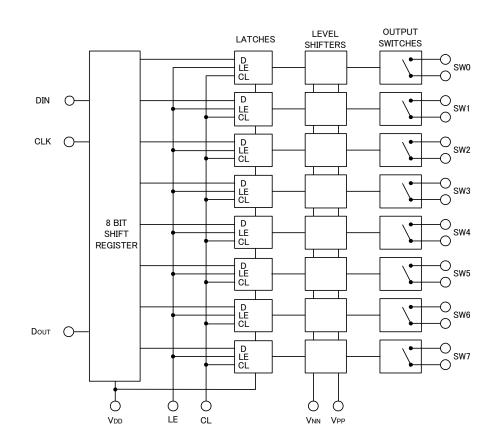

Fig.1 Block diagram

## 1. General

This Specification shall be applied to the following semiconductor integrated circuit.

- 1) Parts name : ECN3290TF, ECN3290PL, ECN3290FN

- 2) Application : Ultrasound imaging scanner and others

- 3) Structure : Monolithic IC

- 4) Package : TQFP48 (ECN3290TF) QFJ28 (ECN3290PL)

- QFN28 (ECN3290FN)

## 2. Absolute Maximum Ratings

#### Table 1 Absolute Maximum Ratings

| No. | Items                            | Symbol | Terminal            | Values               | Unit | N              | ote     |  |

|-----|----------------------------------|--------|---------------------|----------------------|------|----------------|---------|--|

| 1   | Logic power supply voltage       | VDD    | VDD                 | /DD -0.5 ~ +7V       |      | Ta=25°C        |         |  |

| 2   | VPP-VNN supply voltage           | -      | VPP, VNN            | 220V                 | V    | Ta=25°C        |         |  |

| 3   | VPP Positive high voltage supply | VPP    | VPP                 | -0.5 to VNN+200V     | V    | Ta=25°C        |         |  |

| 4   | VNN negative high voltage supply | VNN    | VNN                 | +0.5 to -200V        | V    | Ta=25°C        |         |  |

| 5   | Logic input voltages             | VDD    | DIN, CLK,<br>CL, LE | -0.5 to VDD+0.3      | V    | Ta=25°C        |         |  |

| 6   | Analog signal range              | -      | SW0 to SW7          | /0 to SW7 VNN to VPP |      | Ta=25°C        |         |  |

| 7   | Operating junction temperature   | Тјор   | -                   | -20 to +125          | °C   |                |         |  |

| 8   | Storage temperature              | Tstg   | -                   | -65 to +150          | °C   |                |         |  |

| 0   | Power dissinction                | Pw     |                     | 1.0                  | W    | TQFP48         | Ta=70°C |  |

| 9   | Power dissipation                | ΓW     | -                   | 1.2                  | vv   | QFJ28<br>QFN28 |         |  |

## 3. Electrical Characteristics

## 3.1 DC Characteristics

|      | Т                                          | able 2 D | DC Char | acteristic | s   |       | Ta=25°                         | C, VDD=5V              |  |

|------|--------------------------------------------|----------|---------|------------|-----|-------|--------------------------------|------------------------|--|

| No.  | Items                                      | Symbol   |         | Spec       |     | Unit  | Tost of                        | onditions              |  |

| INU. | items                                      | Symbol   | Min     | Тур        | Max | Offic |                                |                        |  |

|      |                                            |          | -       | 26         | 38  |       | I SIG=5mA                      | VPP=40V,               |  |

|      |                                            |          | -       | 22         | 27  |       | I SIG=200mA                    | VNN=-160V              |  |

| 1    | Small signal switch on resistance          | RONS     | -       | 22         | 27  | Ω     | I SIG=5mA                      | VPP=100V,              |  |

|      |                                            |          | -       | 18         | 24  |       | I SIG=200mA                    | VNN=-100V              |  |

|      |                                            |          | -       | 20         | 25  |       | I SIG=5mA                      | VPP=160V,              |  |

|      |                                            |          | -       | 16         | 25  |       | I SIG=200mA                    | VNN=-40V               |  |

| 2    | Small signal switch on resistance matching | ∆RONS    | -       | 5          | 20  | %     | VPP=100V, VNN=-100V<br>ISW=5mA |                        |  |

| 3    | Large signal switch on resistance          | RONL     | -       | 20         | _   | Ω     | VPP=100V<br>VNN=-100V          | I SIG=1A               |  |

| 4    | Switch off leakage per switch              | ISOL     | -       | 1.0        | 10  | μA    | VSIG=VPP-10V<br>or VNN+10V     | ,                      |  |

| 5    | DC offset switch (off)                     | DCOFF    | -       | 10         | 100 | mV    | $RL=100k\Omega$                |                        |  |

| 6    | DC offset switch (on)                      | DCON     | -       | 10         | 100 | mV    | RL=100kΩ                       |                        |  |

| 7    | Positive HV supply current                 | IPPQ1    | -       | 10         | 50  | μA    | All SWs off                    |                        |  |

| 8    | Negative HV supply current                 | INNQ1    | -       | -10        | -50 | μA    | All SWs off                    |                        |  |

| 9    | Positive HV supply current                 | IPPQ2    | -       | 10         | 50  | μA    | All SWs on, IS                 | W=5mA                  |  |

| 10   | Negative HV supply current                 | INNQ2    | -       | -10        | -50 | μA    | All SWs on, IS                 | W=5mA                  |  |

|      |                                            |          | -       | -          | 7.0 |       | VPP=40V<br>VNN=-160V           | 50kHz output           |  |

| 11   | IPP Supply current                         | IPP      | -       | -          | 5.0 | mA    | VPP=100V<br>VNN=-100V          | switching<br>frequency |  |

|      |                                            |          | -       | -          | 5.0 |       | VPP=160V<br>VNN=-40V           | without load           |  |

|      |                                            |          | -       | -          | 7.0 |       | VPP=40V<br>VNN=-160V           | 50kHz output           |  |

| 12   | INN Supply current                         | INN      | -       | -          | 5.0 | mA    | VNN=-100V                      | switching<br>frequency |  |

|      |                                            |          | -       | -          | 5.0 |       | VPP=160V<br>VNN=-40V           | without load           |  |

| 13   | Logic supply average current               | IDD      | -       | -          | 4.0 | mA    | fCLK=5MHz,VD                   | D=5.0V                 |  |

| 14   | Logic supply quiescent current             | IDDQ     | -       | -          | 10  | μΑ    |                                |                        |  |

| 15   | Data out source current                    | ISOR     | 0.45    | 0.70       | -   | mA    | VOUT=VDD-0.                    | 7V                     |  |

| 16   | Data out sink current                      | ISINK    | 0.45    | 0.70       | -   | mA    | VOUT=0.7V                      |                        |  |

### 3.2 AC Characteristics

|     |                              | Table 3  | AC Cha | aracteris | tics | Ta=25°C, VDD=5V |                               |  |  |

|-----|------------------------------|----------|--------|-----------|------|-----------------|-------------------------------|--|--|

| No. | Items                        | Symbol   |        | Spec      |      | Unit            | Test conditions               |  |  |

| NO. | nems                         | Symbol   | Min    | Тур       | Max  | Unit            | Test conditions               |  |  |

| 1   | SW Turn on time              | tON 5.0  |        |           |      | μS              | VSIG=VPP-10V, RL=10k $\Omega$ |  |  |

| 2   | SW Turn off time             | tOFF 5.0 |        |           |      | μs              | VSIG=VPP-10V, RL=10k $\Omega$ |  |  |

| 3   | Clock frequency              | fCLK     | fCLK   |           |      | MHz             | 50% duty cycle, fData=fCLK/2  |  |  |

| 4   | Clock delay time to data out | tDO      | 30     | -         | 85   | ns              | DOUT terminal                 |  |  |

|     |                              | +VSPK    | -      | -         | 150  |                 | VPP=40V, VNN=-160V,           |  |  |

|     |                              | -VSPK    | -      | -         | -200 |                 | RL=50Ω                        |  |  |

| 5   | Output voltage apika         | +VSPK    | -      | -         | 150  | mV              | VPP=100V, VNN=-100V,          |  |  |

| 5   | Output voltage spike         | -VSPK    | -      | -         | -200 | mv              | RL=50Ω                        |  |  |

|     |                              | +VSPK    | -      | -         | 150  |                 | VPP=160V, VNN=-40V,           |  |  |

|     | -                            | -VSPK    | -      | -         | -200 |                 | RL=50Ω                        |  |  |

| Table 4 AC Characteristics | (for | reference | purpose | only) | Ta=25°C, VDD=5V |

|----------------------------|------|-----------|---------|-------|-----------------|

|----------------------------|------|-----------|---------|-------|-----------------|

| No.  | Itomo                     | Symbol    |                    | Spec |     | Unit | Conditions               |

|------|---------------------------|-----------|--------------------|------|-----|------|--------------------------|

| INO. | Items                     | Symbol    | Min                | Тур  | Max | Unit | Conditions               |

| 1    | Off capacitance SW to GND | CSG (off) | G (off) - 9 - pF 0 |      |     |      | 0V, 1MHz                 |

| 2    | On Capacitance SW to GND  | CSG (on)  | - 14 -             |      |     | pF   | 0V, 1MHz                 |

| 3    | SW off isolation          | ко        | -30                | -33  | -   | dB   | f=5MHz, 1kΩ//15pF load   |

| 3    |                           | ĸŬ        | -54                | -60  | -   | dB   | f=5MHz, 50Ω load         |

| 4    | SW Crosstalk              | KCR       | -54                | -60  | -   | dB   | f=5MHz, 50 $\Omega$ load |

Note: These items are not tested when shipped.

## 4. Recommended Operating Conditions

Please operate in use within the limit of recommended operating conditions detailed in Table 5.

|    | Table 5 Reco                       | mmended Oper | ating Conditions          |

|----|------------------------------------|--------------|---------------------------|

| No | Items                              | Symbol       | Recommended Value         |

| 1  | Logic power supply voltage         | VDD          | 4.5V to 5.5V              |

| 2  | Positive high voltage supply       | VPP          | 40V to VNN+200V           |

| 3  | Negative high voltage supply       | VNN          | -40V to -160V             |

| 4  | High-level input voltage           | VIH          | VDD - 1.5V to VDD         |

| 5  | Low-level input voltage            | VIL          | 0V to 1.5V                |

| 6  | Analog signal voltage peak to peak | VSIG         | VNN+10V to VPP-10V        |

| 7  | Operating free air-temperature     | Та           | 0°C to 70°C               |

| 8  | Switching frequency                | fsw          | 50kHz max, Duty Cycle=50% |

| 9  | Set up time for LE                 | tSD          | Min.75ns                  |

| 10 | Pulse width of LE                  | tWLE         | Min.75ns                  |

| 11 | Time width of CL                   | tWCL         | Min.60ns                  |

| 12 | Set up time DATA to Clock          | tSU          | Min.10ns                  |

| 13 | Hold time DATA from Clock          | th           | Min.20ns                  |

| 14 | Maximum VSIG Slew Rate             | dV/dt        | Max.30V/ns                |

Attention ;

- 1) Power up/down sequence of power supply is arbitrary except GND terminal of IC must be poweredup first and powered-down last.

- 2) It is indispensable to make there are not to exceed a maximum rated voltage by the occurrence of the excessive voltage in case of investing and cutting of the power supply.

## 5. Test Circuit

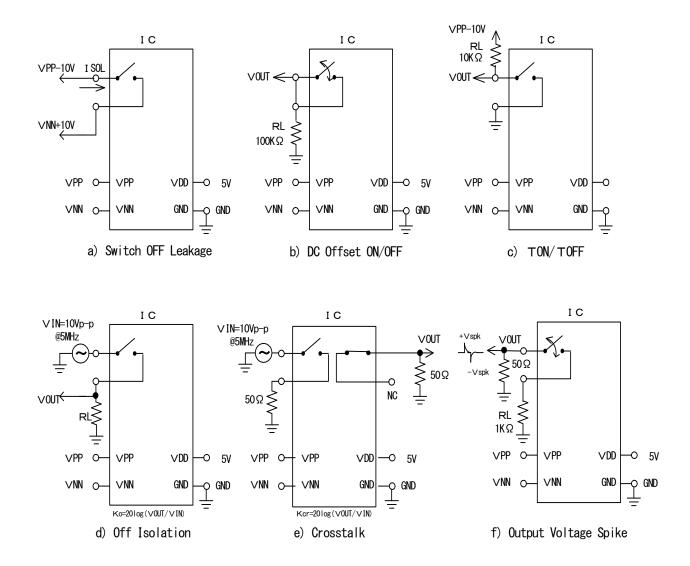

Fig. 2 Test Circuit

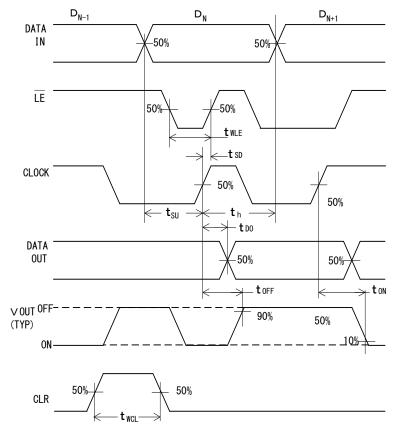

## 6. Timing Waveforms

7. Truth Table

### Table 6 Truth table

| D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | LE | CL | SW0 | SW1 | SW2 | SW3     | SW4     | SW5 | SW6 | SW7 |

|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|---------|---------|-----|-----|-----|

| L  |    |    |    |    |    |    |    | L  | L  | OFF |     |     |         |         |     |     |     |

| Н  |    |    |    |    |    |    |    | L  | L  | ON  |     |     |         |         |     |     |     |

|    | L  |    |    |    |    |    |    | L  | L  |     | OFF |     |         |         |     |     |     |

|    | Н  |    |    |    |    |    |    | L  | L  |     | ON  |     |         |         |     |     |     |

|    |    | L  |    |    |    |    |    | L  | L  |     |     | OFF |         |         |     |     |     |

|    |    | Н  |    |    |    |    |    | L  | L  |     |     | ON  |         |         |     |     |     |

|    |    |    | L  |    |    |    |    | L  | L  |     |     |     | OFF     |         |     |     |     |

|    |    |    | Н  |    |    |    |    | L  | L  |     |     |     | ON      |         |     |     |     |

|    |    |    |    | L  |    |    |    | L  | L  |     |     |     |         | OFF     |     |     |     |

|    |    |    |    | Н  |    |    |    | L  | L  |     |     |     |         | ON      |     |     |     |

|    |    |    |    |    | L  |    |    | L  | L  |     |     |     |         |         | OFF |     |     |

|    |    |    |    |    | Н  |    |    | L  | L  |     |     |     |         |         | ON  |     |     |

|    |    |    |    |    |    | L  |    | L  | L  |     |     |     |         |         |     | OFF |     |

|    |    |    |    |    |    | Н  |    | L  | L  |     |     |     |         |         |     | ON  |     |

|    |    |    |    |    |    |    | L  | L  | L  |     |     |     |         |         |     |     | OFF |

|    |    |    |    |    |    |    | Н  | L  | L  |     |     |     |         |         |     |     | ON  |

| Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Н  | L  |     |     | Ho  | ld prev | ious st | ate |     |     |

| Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Н  | OFF | OFF | OFF | OFF     | OFF     | OFF | OFF | OFF |

## 8. Pin Configuration

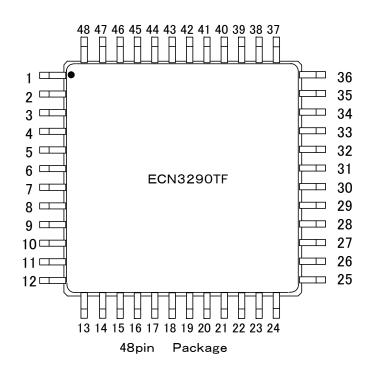

8.1 ECN3290TF TQFP48 (48Pin TQFP)

|     | Table7.   | Pin Configurat | ion       |

|-----|-----------|----------------|-----------|

| Pin | Functions | Pin            | Functions |

| 1   | SW5       | 25             | VNN       |

| 2   | N/C       | 26             | N/C       |

| 3   | SW4       | 27             | N/C       |

| 4   | N/C       | 28             | GND       |

| 5   | SW4       | 29             | VDD       |

| 6   | N/C       | 30             | N/C       |

| 7   | N/C       | 31             | N/C       |

| 8   | SW3       | 32             | N/C       |

| 9   | N/C       | 33             | DIN       |

| 10  | SW3       | 34             | CLK       |

| 11  | N/C       | 35             | LE        |

| 12  | SW2       | 36             | CLR       |

| 13  | N/C       | 37             | DOUT      |

| 14  | SW2       | 38             | N/C       |

| 15  | N/C       | 39             | SW7       |

| 16  | SW1       | 40             | N/C       |

| 17  | N/C       | 41             | SW7       |

| 18  | SW1       | 42             | N/C       |

| 19  | N/C       | 43             | SW6       |

| 20  | SW0       | 44             | N/C       |

| 21  | N/C       | 45             | SW6       |

| 22  | SW0       | 46             | N/C       |

| 23  | N/C       | 47             | SW5       |

| 24  | VPP       | 48             | N/C       |

8.2

# ECN3290TF/PL/FN

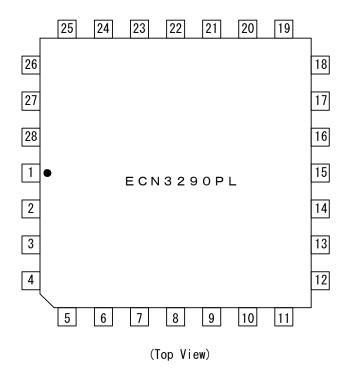

| ECN32    | 90PL QFJ28 | (28Pin J-Lead)    |            |

|----------|------------|-------------------|------------|

|          | Table 8.   | Pin Configuration | ons        |

| Pin      | Functions  | Pin               | Functions  |

| 1        | SW3        | 15                | N/C        |

| 2        | SW3        | 16                | DIN        |

| 3        | SW2        | 17                | CLK        |

| 4        | SW2        | 18                | LE         |

| 5        | SW1        | 19                | CL         |

| 6        | SW1        | 20                | DOUT       |

| 7        | SW0        | 21                | SW7        |

| 8        | SW0        | 22                | SW7        |

| 9        | N/C        | 23                | SW6        |

| 10       | VPP        | 24                | SW6        |

| 11       | N/C        | 25                | SW5        |

| 12       | VNN        | 26                | SW5        |

| 13       | GND        | 27                | SW4        |

| 14       | VDD        | 28                | SW4        |

| 12<br>13 | VNN<br>GND | 26<br>27          | SW5<br>SW4 |

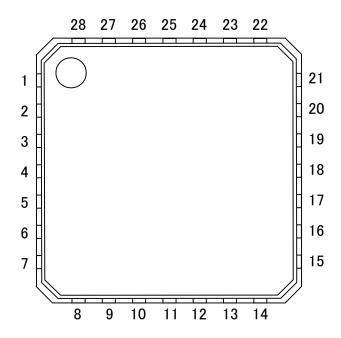

8.3 ECN3290FN QFN28 (28Pin No-Lead)

|     | Table 9.  | Pin Configurat | ions      |

|-----|-----------|----------------|-----------|

| Pin | Functions | Pin            | Functions |

| 1   | SW5       | 15             | N/C       |

| 2   | SW4       | 16             | VNN       |

| 3   | SW4       | 17             | GND       |

| 4   | SW3       | 18             | VDD       |

| 5   | SW3       | 19             | DIN       |

| 6   | SW2       | 20             | CLK       |

| 7   | N/C       | 21             | LE        |

| 8   | SW2       | 22             | CL        |

| 9   | SW1       | 23             | DOUT      |

| 10  | SW1       | 24             | SW7       |

| 11  | SW0       | 25             | SW7       |

| 12  | SW0       | 26             | SW6       |

| 13  | N/C       | 27             | SW6       |

| 14  | VPP       | 28             | SW5       |

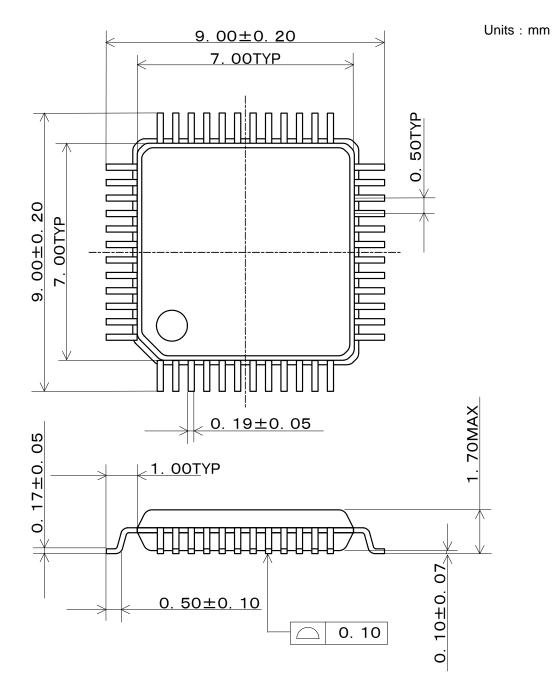

## 9. Package Outline

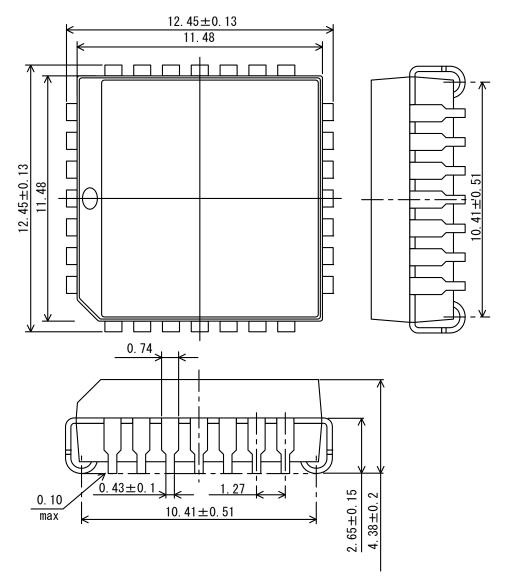

## 9.1 ECN3290TF

Fig.4 Package Outline (48pin TQFP Package)

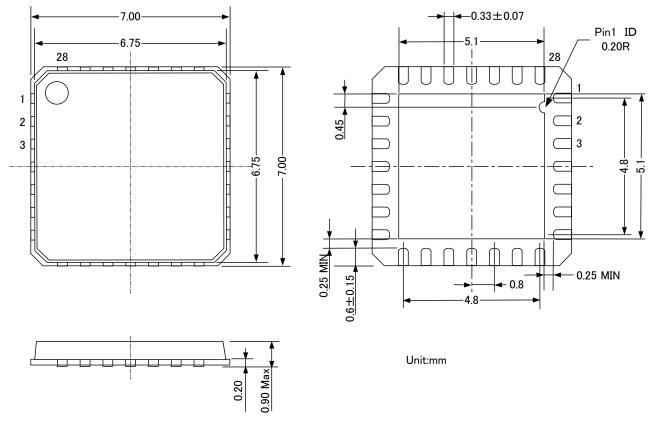

9.2 ECN3290PL

Fig.4 Package Outline (28pin J-Lead Package)

### 9.3 ECN3290FN

Fig.5 Package Outline (Quad Flat No-Lead 28pin)

#### Note ;

a) Connection of tab

A tab of the back of a QFN package and each terminal of IC are not connected. Please use the tab as open, or use it for GND, connecting.

Do not impress the voltage beyond 220V of a rated value between a tab and each terminal of IC.

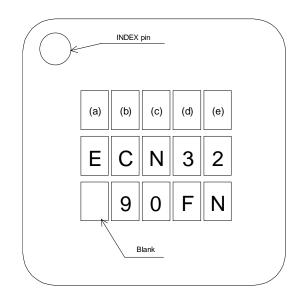

## 10. Marking spec

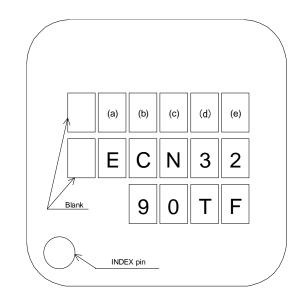

10.1 ECN3290TF

### Lot numbering rule

(a): Year code (Least significant digit of Assembled year (A.D.))

(b): Month code (Refer to following table.)

|               |   | ( |   | - ···· · · · · · · · · · · · · · · · · |   |   |   |   |   |    |    |    |

|---------------|---|---|---|----------------------------------------|---|---|---|---|---|----|----|----|

| Month         | 1 | 2 | 3 | 4                                      | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| Month<br>code | А | В | С | D                                      | Е | к | L | М | Ν | х  | Y  | Z  |

(c),(d),(e): Serial number within year/month code

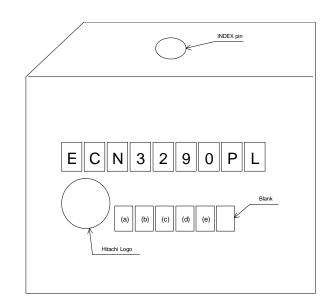

### 10.2 ECN3290PL

This product indicates "F" (d) of the following lot number display, or (e) for the discernment, which is a lead free correspondence article.

#### Lot numbering rule

(a): Year code (Least significant digit of Assembled year (A.D.))

(b): Month code (Refer to following table.)

| ,             |   | 1 |   |   |   |   |   |   |   |    |    |    |

|---------------|---|---|---|---|---|---|---|---|---|----|----|----|

| Month         | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| Month<br>code | А | В | С | D | Е | к | L | М | Ν | х  | Y  | Z  |

(c),(d),(e): Serial number within year/month code

### 10.3 ECN3290FN

Lot numbering rule

(a): Year code (Least significant digit of Assembled year (A.D.))

(b): Month code (Refer to following table.)

| ( )           |   |   |   | 0 | , |   |   |   |   |    |    |    |

|---------------|---|---|---|---|---|---|---|---|---|----|----|----|

| Month         | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| Month<br>code | А | В | С | D | Е | к | L | М | Ν | х  | Y  | Z  |

(c),(d),(e): Serial number within year/month code

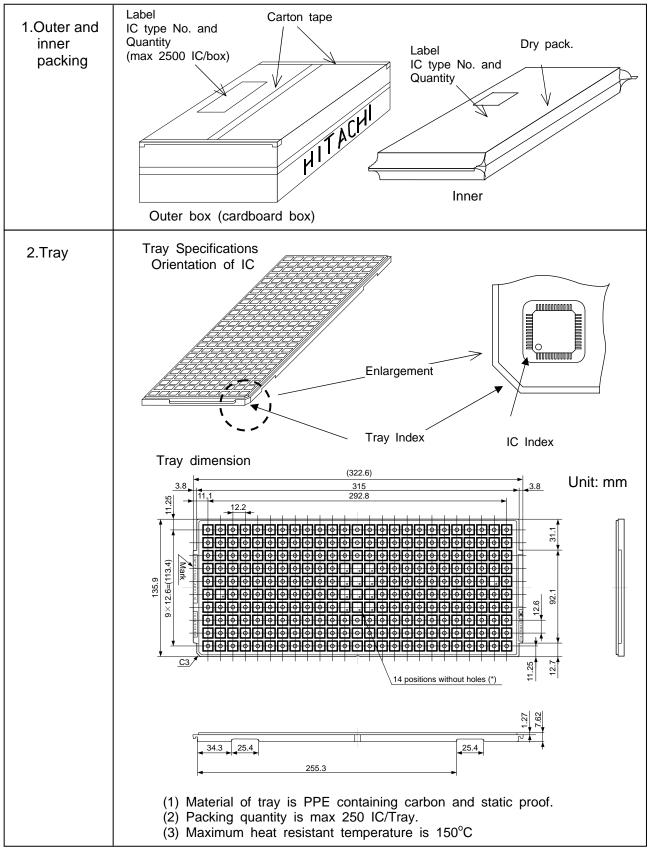

## 11. Packing Form

### 11.1 ECN3290TF

Packaging details are as shown below.

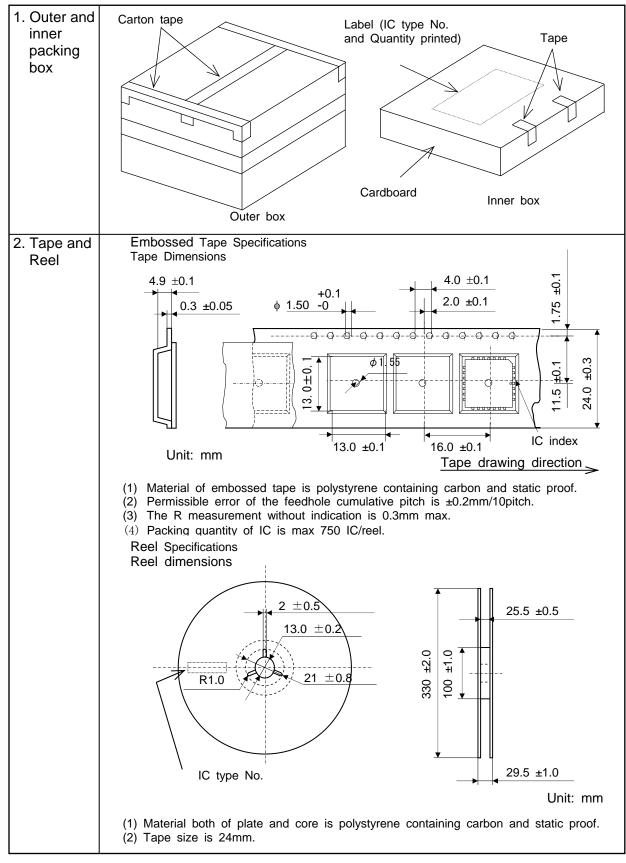

### 11.2 ECN3290PL

Packaging details are as shown below. IC is taped and reeled in inner box, wrapped by outer cardboard box.

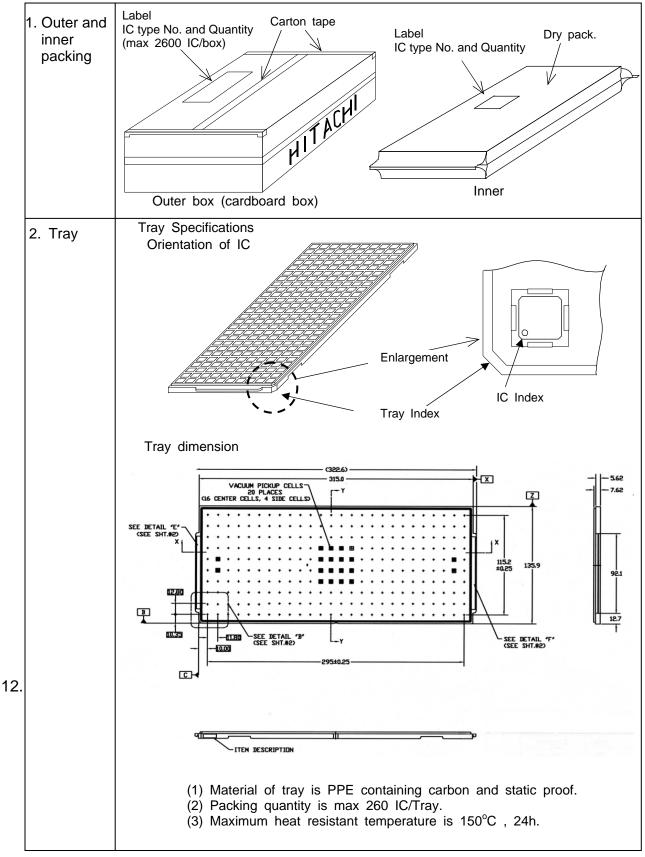

### 11.3 ECN3290FN

Packaging details are as shown below.

## 12. Inspection

Hundred percent inspections shall be conducted on electric characteristics.

### 13. Important Notice

- 13.1 Hitachi warrants performance of its power semiconductor products (hereinafter called "products") to the specifications applicable at the time of sale in accordance with the Product Specification. Testing and other quality control techniques are utilized to the extent Hitachi needs to meet specifications described in the Product Specification. Specific testing of all parameters of each device is not necessarily performed, except those mandated by related laws and/or regulations.

- 13.2 Should any claim be made within one month of product delivery about products' failure to meet performance described in the Product Specification, all the products in relevant lot(s) shall be retested and re-delivered. Products delivered more than one month before of such claim shall not be counted for such response.

- 13.3 Hitachi assumes no obligation or any way of compensation should any fault about customer's goods using products be found in marketplace. Only in such a case fault of Hitachi is evident and products concerned do not meet the Product Specification, compensation shall be conducted if claimed within one year of product delivery up to in the way of product replacement or payment of equivalent amount.

- 13.4 Hitachi reserves the right to make changes in the Product Specification and to discontinue mass production of the relevant products without notice. Customers are advised before purchasing to confirm specification of the product of inquiry is the latest version and that the relevant product is on mass production status in such a case purchasing is suspended for one year or more.

- 13.5 In no event shall Hitachi be liable for any damage that may result from an accident or any other cause during operation of the user's units according to this Product Specification. Hitachi assumes no responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in this Product Specification.

- 13.6 No license is granted by this Product Specification under any patents or other rights of any third party or Hitachi Power Semiconductor Device, Ltd.

- 13.7 This Product Specification may not be reproduced or duplicated, in any form, in whole or in part, without the expressed written permission of Hitachi Power Semiconductor Device, Ltd.

- 13.8 The products (technologies) described in this Product Specification are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.

### 14. Cautions

- 14.1 Customers are advised to follow the below cautions to protect semiconductor from electrical static discharge (ESD).

- a) IC needs to be dealt with caution to protect from damage by ESD. Material of container or any device to carry semiconductor devices should be free from ESD, which may be caused by vibration while transportation. To use electric-conductive container or aluminum sheet is recommended as an effective countermeasure.

- b) Those what touch semiconductor devices such as work platform, machine and measuring and test equipment should be grounded.

- c) Workers should be grounded connecting with high impedance around  $100k\Omega$  to  $1M\Omega$  while dealing with semiconductor to avoid damaging IC by electric static discharge.

- d) Friction with other materials such as a high polymer should not be caused.

- e) Attention is needed so that electric potential will be kept on the same level by short circuit terminals when PC board with mounted IC is carried and that vibration or friction might not occur.

- f) Air conditioningis needed so that humidity should not drop.

- 14.2 Refer to the latest version of "Instructions for Use of Hitachi High-Voltage Monolithic ICs" for the other precautions and instructions on how to deal with products.

- 14.3 Regardless of changes in external conditions during use, "absolute maximum ratings" should never be exceeded in designing electronic circuits that employ products. In a case absolute maximum ratings are exceeded, products may be damaged or destroyed. In no event shall Hitachi be liable for any failure in products or any secondary damage resulting from use at a value exceeding the absolute maximum ratings.

- 14.4 Products may experience failures due to accident or unexpected surge voltages. Accordingly, adopt safe design features, such as redundancy or prevention of erroneous action, to avoid extensive damage in the event of a failure.

- 14.5 Products are not designed, manufactured, or warranted to be suitable for use where extremely high reliability is required (such as use in nuclear power control, aerospace and aviation, traffic equipment, life-support-related medical equipment, fuel control equipment and various kinds of safety equipment).

Inclusion of products in such application shall be fully at the risk of customers. Hitachi Power Semiconductor Device, Ltd. assumes no liability for applications assistance, customer product design, or performance. In such cases it is advised customers ensure circuit and/or product safety by using semiconductor devices that assures high reliability or by means of user's fail-safe precautions or other arrangement.

- (If a semiconductor device fails, there may be cases in which the semiconductor device, wiring or wiring pattern will emit smoke or cause a fire or in which the semiconductor device will burst.)

- 14.6 Lead-free solder is used for coating pins and the tab of this IC. Refer to the latest version of "Instructions for Use of Hitachi High-Voltage Monolithic ICs" for soldering conditions.

#### 14.7 Storage

a) Products are using anti-moisture packing to avoid absorption before solder installation. The epoxy resin used in plastic package has moisture-absorption characteristics. When products are stored in high humidity areas, moisture absorption is unavoidable. If a large amount of water is absorbed, it quickly turns into steam during solder installation, which causes package cracking. So, Moisture absorbed product has to remove moisture absorbed like as baking process.

Please refer to the followings and the Clause 6.2, the latest version of "Instructions for Use of Hitachi High-Voltage Monolithic ICs" for handling before and/or after opening the antimoisture packing.

- b) For strorage before opening the anti-moisture packing

Store products before opening the anti-moisture packing in the room where temparature and humidity are controlled. Control the Storing environment is 5~35°C and 45~75% RH.

- c) For handling after opening the anti-moisture packing Storage conditions after opening the anti-moisture packing are follows;

#### Standard storage conditions after opening the anti-moisture packing

| Items        | Conditions       | Remarks                                                             |  |  |  |  |  |  |  |

|--------------|------------------|---------------------------------------------------------------------|--|--|--|--|--|--|--|

| Temperature  | 5 to 30 °C       |                                                                     |  |  |  |  |  |  |  |

| Humidity     | 70% RH or less   |                                                                     |  |  |  |  |  |  |  |

| Storage time | within 168 hours | The time from opening the packing to finishing the reflow soldering |  |  |  |  |  |  |  |

When storing products for long periods, use low humidity storage box (30%RH) and so on. After taking products out from storage box, store products on the condition in the abovementioned table. It's the same as after opening the anti-moisture packing

d) Baking

Baking is necessary in the following cases;

- (1) When a blue color indicator placed in a desiccant (silica gel) cannot be seen.

- (2) When specified storage time has elapsed or it may have elapsed.

- ${\rm e})$  Baking condition

Baking conditions is follows;

Baking temperature: 125 °C, Baking time: 16 to 24 hours

When baking products before soldering, use the heat-resistance tray (it's marked "HEAT PROOF").

#### $f)\;$ Desiccant in the anti-moisture packing

The desiccant (silica gel) is enclosed in the anti-moisture packing, in order to moisture exclusion. If a humidity indicator card is packed in an anti-moisture pack (dry pack), it can check the rate of moisture absorption.

The indicator shows deep blue before moisture absorption. When moisture is adsorbed, it gradually discolors. After the moisture absorbent ability completely lost, the indicator becomes lavender (pink).

## Precautions for Safe Use and Notices

If semiconductor devices are handled inappropriate manner, failures may result. For this reason, be sure to read the latest version of "Instructions for Use of Hitachi High-Voltage Monolithic ICs" before use.

This mark indicates an item about which caution is required.

CAUTION

This mark indicates a potentially hazardous situation which, if not avoided, may result in minor or moderate injury and damage to property.

## CAUTION

- (1) Regardless of changes in external conditions during use "absolute maximum ratings" should never be exceed in designing electronic circuits that employ semiconductors. In the case of pulse use, furthermore,"safe operating area (SOA)"precautions should be observed.

- (2) Semiconductor devices may experience failures due to accident or unexpected surge voltages. Accordingly, adopt safe design features, such as redundancy or prevention of erroneous action, to avoid extensive damage in the event of a failure.

- (3) In cases where extremely high reliability is required (such as use in nuclear power control, aerospace and aviation, traffic equipment, life-support-related medical equipment, fuel control equipment and various kinds of safety equipment), safety should be ensured by using semiconductor devices that feature assured safety or by means of user's fail-safe precautions or other arrangement. Or consult Hitachi's sales department staff.

(If a semiconductor devices fails, there may be cases in which the semiconductor device, wiring or wiring pattern will emit smoke or cause a fire or in which the semiconductor device will burst)

## NOTICES

- 1. This Data Sheet contains the specifications, characteristics (in figures and tables), dimensions and handling notes concerning power semiconductor products (hereinafter called "products") to aid in the selection of suitable products.

- 2. The specifications and dimensions, etc. stated in this Data Sheet are subject to change without prior notice to improve products characteristics. Before ordering, purchasers are advised to contact Hitachi's sales department for the latest version of this Data Sheet and specifications.

- 3. In no event shall Hitachi be liable for any damage that may result from an accident or any other cause during operation of the user's units according to this Data Sheet. Hitachi assumes to responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in this Data Sheet.

- 4. In no event shall Hitachi be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.

- 5. No license is granted by this Data Sheet under any patents or other rights of any third party or Hitachi Power Semiconductor Device, Ltd.

- 6. This Data Sheet may not be reproduced or duplicated, in any form, in whole or in part, without the expressed written permission of Hitachi Power Semiconductor Device, Ltd.

- 7. The products (technologies) described in this Data Sheet are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.

Refer to the following website for the latest information. Consult Hitachi's sales department staff if you have any questions.

http://www.hitachi-power-semiconductor-device.co.jp/en/